Semiconductor industry shifts to modular chiplet designs, promising flexibility but facing integration challenges as components from different vendors must work together seamlessly.

Drivetech Partners

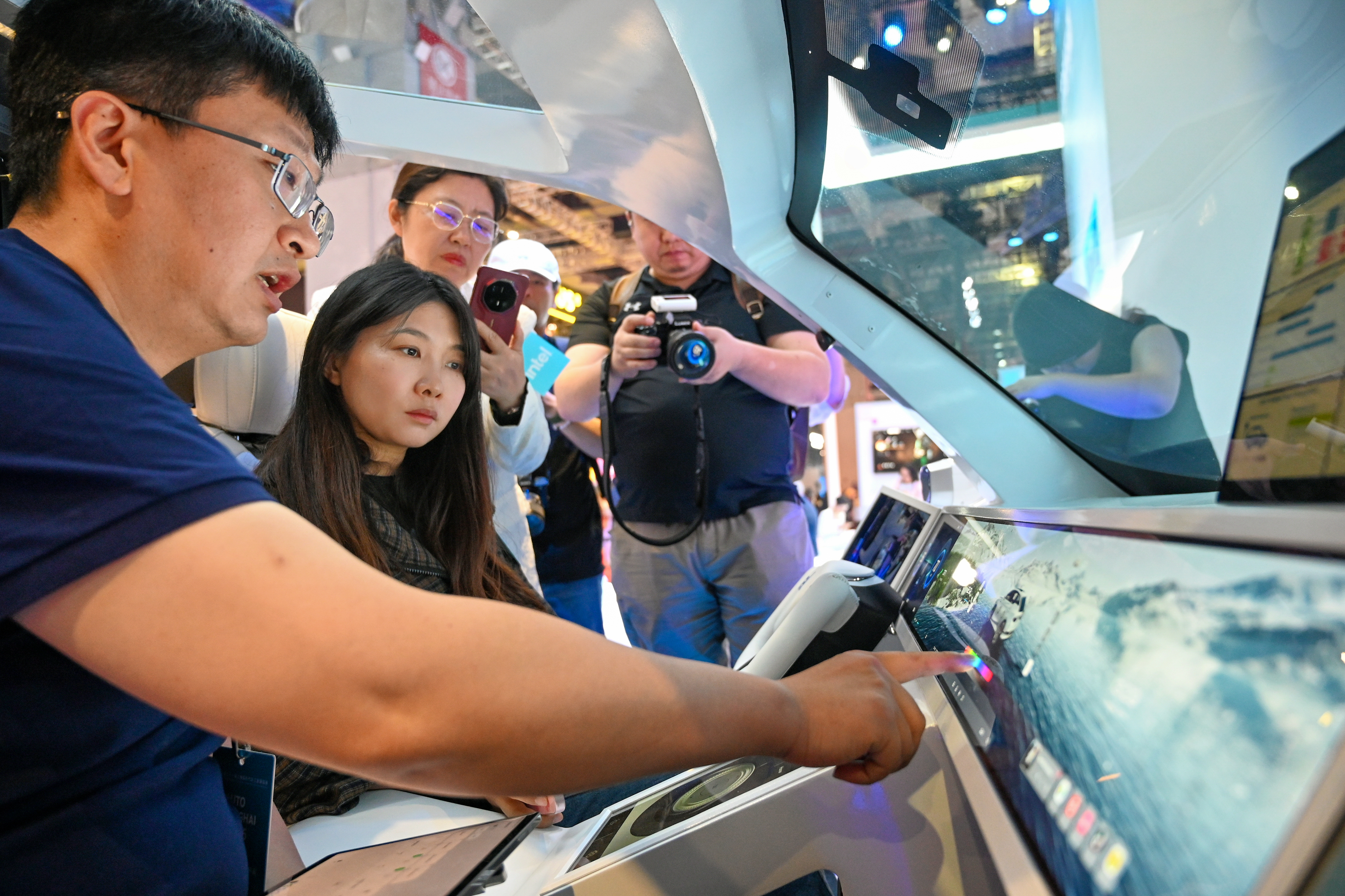

The semiconductor industry is experiencing a paradigm shift as chiplet-based architectures replace traditional monolithic chip designs with modular components that can be mixed and matched from various vendors. This transition promises greater flexibility, cost efficiency, and performance, but introduces significant challenges around ensuring that chiplets from different manufacturers can seamlessly integrate and function reliably together.

Key Takeaways

Chiplet-based designs are revolutionizing semiconductor manufacturing by enabling modular integration of specialized components

Different vendor design methodologies and manufacturing processes create interoperability barriers that limit the potential of multi-vendor chiplet systems

Industry standards like Universal Chiplet Interconnect Express (UCIe) are emerging to address integration challenges

Standardized quality assurance protocols are essential for reliability and consumer trust in mixed-vendor chiplet products

Companies embracing open standards will gain competitive advantages through faster innovation cycles and more flexible designs

The Evolution of Chiplet Architecture

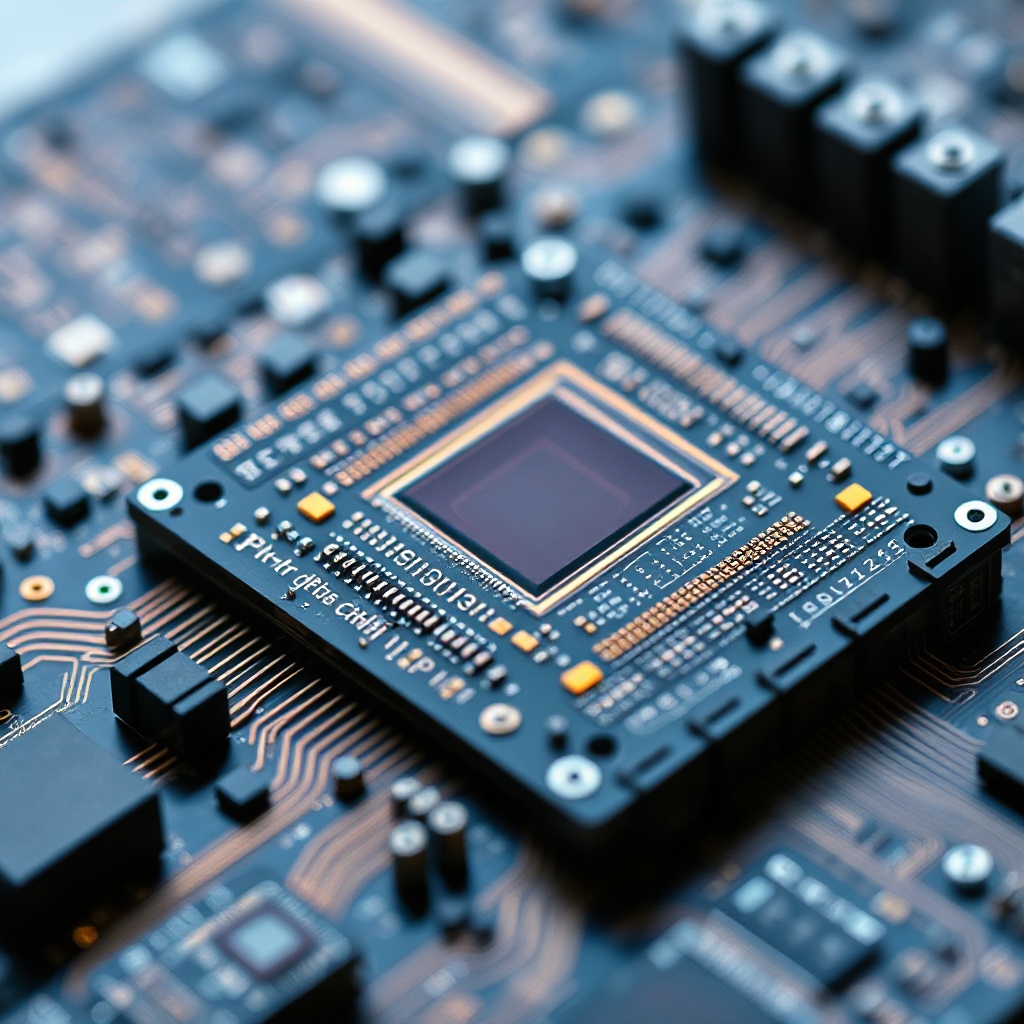

Chiplets represent a fundamental architectural shift in the semiconductor industry. Instead of creating a single, large monolithic chip, manufacturers now design smaller, specialized silicon dies (chiplets) that can be assembled into complex systems on a substrate or interposer. This approach brings several key advantages, including improved yield (more functional dies per wafer), cost efficiency through mixing process nodes, and enhanced performance scalability.

The chiplet approach allows for optimized combinations of heterogeneous components such as CPUs, memory, and I/O interfaces, each built using the most appropriate process technology. Leading semiconductor companies like AMD, Intel, and Nvidia have already implemented chiplet-based designs in their latest products, driving significant market growth and innovation in this space.

The Multi-Vendor Integration Challenge

While the chiplet concept is promising, combining chiplets from different vendors introduces significant complexity. Each supplier typically uses unique Electronic Design Automation (EDA) tools, design verification flows, and architectures, creating substantial integration barriers. The challenges stem from incompatible interface standards, varying electrical characteristics, and different packaging and bonding requirements.

Physical implementation is further complicated by the variety of integration methods used across the industry, from 2.5D and 3D stacking to different bonding technologies. Manufacturing variations between vendors using different process nodes (e.g., 5nm logic combined with 7nm memory) directly impact overall system performance and reliability.

For successful integration, engineers must address numerous physical challenges including mechanical stress, thermal dissipation, and electrical integrity across interfaces. These considerations become exponentially more complex in multi-vendor scenarios where proprietary approaches often clash.

Packaging and Interconnect Technology Barriers

One of the most critical aspects of chiplet integration is the die-to-die interconnect technology used to communicate between components. These technologies vary widely among suppliers, ranging from microbumps with pitches of 50µm-30µm to advanced hybrid bonding techniques that can achieve much finer pitches down to 5µm. The choice of interconnect technology directly impacts the feasibility of die stacking and overall system performance.

Different process nodes and packaging approaches from various vendors add layers of complexity to integration efforts. Manufacturing variations between suppliers can lead to yield and reliability issues in the final product. Physical compatibility challenges include thermal management, mechanical stress, and maintaining signal integrity across interfaces – with each supplier potentially using proprietary approaches to these challenges.

Quality Assurance and Testing Hurdles

Perhaps the most underappreciated challenge in multi-vendor chiplet systems is the lack of standardized quality assurance protocols. This deficiency significantly limits scalability and reliability. Verification, emulation, and validation must occur at both the individual chiplet level and the integrated system level, requiring coordination across company boundaries.

Current challenges in the quality assurance space include the absence of:

Universal testing standards to detect, isolate, and repair defective chiplets

Security and traceability protocols ensuring chiplet provenance throughout the supply chain

'Fail-fast' protocols and continuous integration principles for rapid detection of issues

Inconsistent QA and reliability frameworks across suppliers pose serious risks to overall system dependability. For chiplet architectures to succeed in high-volume manufacturing, the industry needs comprehensive, interoperable testing frameworks that all vendors can adopt.

Industry Standardization Initiatives

Recognizing these challenges, the semiconductor industry has launched several standardization initiatives aimed at enabling multi-vendor chiplet integration. The Universal Chiplet Interconnect Express (UCIe) stands out as a leading open industry standard for die-to-die interconnects, designed specifically to enable interoperability between chiplets from different vendors. The UCIe Management Transport Protocol supports critical services like security and power management across chiplet boundaries.

Other important standards include:

Advanced Interface Bus (AIB), developed by Intel, providing an open interface for data exchange among chiplets

Open Domain-Specific Architecture (ODSA) guidelines for uniform chiplet modeling and trading

NIST and CHIPS for America initiatives driving security, traceability, and universal testing standards

Major players like AMD are collaborating with EDA vendors and third-party suppliers to create unified verification frameworks. These industry standards bodies are also working to establish certification frameworks that can validate multi-vendor compatibility, a crucial step toward building trust in the chiplet ecosystem.

Supply Chain and Trust Considerations

Reliable, certified chiplet integration is essential for accelerating innovation across multiple markets including AI, data centers, edge computing, and consumer devices. The industry is developing standardized chiplet models, bare dielet warehousing, and discovery methodologies to enable seamless assembly and reuse across vendors.

The current lack of supply chain transparency and consistent quality standards creates significant trust issues in multi-vendor scenarios. Security and traceability protocols are becoming increasingly important to ensure chiplet provenance – knowing exactly where each component came from and how it was manufactured.

Standardized certification frameworks are necessary to build trust in multi-supplier chiplet ecosystems. The development of robust supply chains dependent on standardization will ultimately enable competitive advantages through more rapid innovation and flexible design options.

The Future of Multi-Vendor Chiplet Ecosystems

Effective standardization will boost scalability, enable robust supply chains, and increase customer confidence in multi-vendor integration. For the chiplet approach to reach its full potential, the industry needs automation, modular design environments, and robust testing methodologies for rapid, reliable integration at scale.

The ongoing development of standards focuses on several key areas:

Chiplet modeling and simulation for pre-integration verification

Physical and electrical interfaces for seamless connection

Testing and quality assurance protocols across vendors

Security and provenance verification throughout the supply chain

The success of chiplet architectures depends on industry-wide cooperation and adoption of open standards. Companies that embrace standardization will gain competitive advantages through faster innovation cycles and more flexible designs, while those that resist may find themselves isolated in an increasingly interconnected semiconductor ecosystem.

As the chiplet revolution continues to gain momentum, solving these multi-vendor interoperability challenges will be crucial to unlocking the full potential of this transformative approach to semiconductor design and manufacturing.

Sources

Synopsys - What are Chiplets?

Semiconductor Engineering - Chiplets: Deep Dive Into Designing, Manufacturing, And Testing

IMEC - Chiplets: piecing together the next generation of chips

TechInsights - Chiplets a new design methodology?

Mark LaPedus - Intel Unveils Chiplet Alliance To Enable New Chip Designs

AMD - Chiplet Architecture White Paper

Semiconductor Engineering - Piecing Together Chiplets

Cadence - An Overview of Chiplets for Systems Designers

NIST - CHIPS R&D Chiplets Interfaces Technical Standards Workshop

SEMI - MRHIEP Final report for publication